A fundamental shift is occurring in AI infrastructure: the performance bottleneck is moving from the accelerator to the CPU. While attention has focused on GPU shortages, new research reveals that inadequate CPU resources are now causing significant latency issues in large language model serving, with time-to-first-token increasing by up to 5.4 times in under-provisioned systems.

The CPU Control Plane Problem

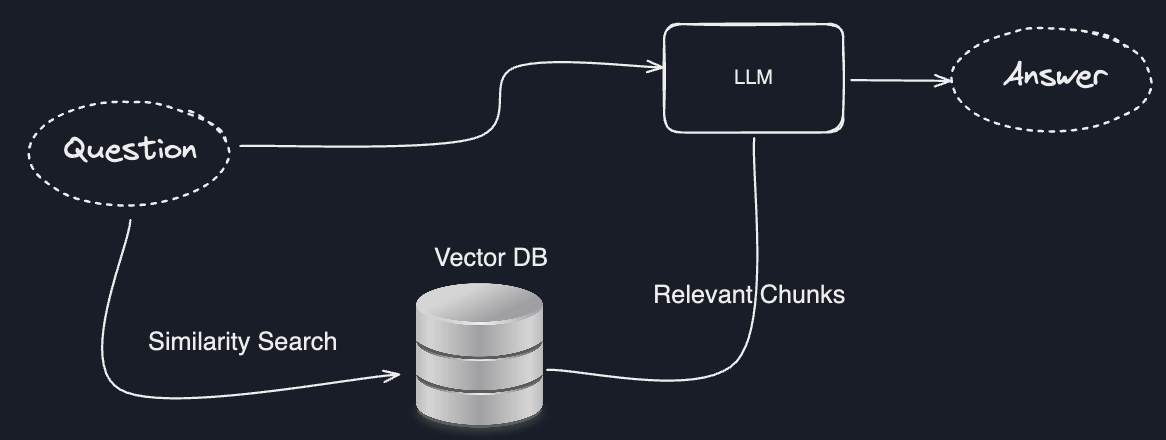

Modern AI inference involves far more than just matrix multiplication on GPUs. The CPU now handles what researchers call the "control plane"—a collection of critical tasks that keep GPU clusters fed and synchronized:

- Tokenization: Converting text to numerical tokens before GPU processing

- Kernel launches: Initiating GPU computation kernels

- Batch scheduling: Managing multiple inference requests efficiently

- Inter-process messaging: Communication between distributed processes

- Storage and networking: Data movement to keep tensor-parallel GPUs busy

A March 2024 study found that moving 4 to 8 GPU LLM servers from minimal CPU allocation to CPU-abundant configurations reduced time-to-first-token by factors ranging from 1.36 to 5.40. In some cases, lean CPU configurations timed out entirely, failing to serve requests.

The Autoregressive Serving Penalty

The problem becomes particularly acute during the decode phase of autoregressive generation. Unlike the parallelizable prefill stage, decode generates tokens sequentially, multiplying host overhead with each token. Research from the TaxBreak paper (March 2024) quantified this penalty: in one setup, generating 10 decode tokens took 188 ms versus just 22 ms for prefill. The same study found that faster CPU single-thread performance reduced host-bound latency by 11-14%.

Structural issues compound the problem. A Georgia Tech paper identified that vLLM's shared-memory broadcast queue—a critical component for distributed inference—could stretch from approximately 12 ms to 228 ms under load. This made the CPU control path roughly five times longer than the GPU compute step, with the problem worsening with tensor parallelism.

Market Consequences: Supply Squeeze and Price Inflation

The technical bottleneck has translated directly into market pressure. According to Reuters reporting, AI-driven server CPU lead times have stretched to six months, with prices rising by more than 10% in some markets. In January 2024, Intel publicly acknowledged it was struggling to meet AI data center CPU demand.

This supply-demand imbalance affects not just procurement but system architecture decisions. Data center operators who previously focused primarily on GPU specifications are now forced to reconsider their entire server architecture, with CPU capabilities becoming a first-order constraint on inference performance.

Arm's Window of Opportunity

The x86 supply crunch creates a strategic opening for Arm-based server CPUs. The opportunity isn't merely architectural preference—it's driven by specific technical requirements of AI workloads:

- Memory bandwidth: AI inference requires moving massive parameter sets and activations

- I/O capacity: High-speed connectivity between CPUs and accelerators

- Power efficiency: Data centers face both power and thermal constraints

- Host-side scheduling: Efficient orchestration of heterogeneous compute

Arm's new AGI (Arm Graviton for Infrastructure) design targets these needs with specifications including 12 DDR5 channels, more than 800 GB/s of memory bandwidth, 96 PCIe Gen6 lanes, and CXL 3.0 support. While independent validation of Arm's rack-scale claims is pending, the architectural focus aligns precisely with the emerging CPU bottleneck pattern.

The Coordination Problem

The deeper insight from recent research is that AI infrastructure is evolving from a pure compute problem to a coordination problem. As model sizes grow and inference becomes distributed across more accelerators, the overhead of coordination—scheduling, communication, data movement—increases disproportionately. This coordination work runs primarily on CPUs, making their performance characteristics critical to overall system efficiency.

gentic.news Analysis

This CPU bottleneck represents the second-order effect of the AI infrastructure buildout we've been tracking. Our coverage of NVIDIA's Blackwell architecture and the ongoing GPU shortage highlighted the primary constraint, but as those systems deploy, attention shifts to supporting infrastructure. This pattern mirrors historical computing transitions where breakthroughs in specialized hardware eventually reveal bottlenecks in general-purpose components.

The Arm opportunity is particularly significant given the historical dominance of x86 in data centers. While Arm has made inroads in cloud instances (AWS Graviton, Azure Cobalt), AI workloads represent a new beachhead where architectural advantages could overcome ecosystem inertia. The timing aligns with increased activity in the custom silicon space—we've covered Google's Axion, AWS Trainium/Inferentia, and Microsoft's Maia—suggesting broader architectural experimentation is underway.

The coordination problem framing is crucial for practitioners. Many teams optimizing inference latency focus exclusively on GPU compute or model architecture, but as this research shows, host-side overhead can dominate end-to-end latency, especially for interactive applications. This suggests a need for more holistic performance analysis tools that capture the entire inference stack, not just accelerator metrics.

Frequently Asked Questions

Why are AI data centers suddenly experiencing CPU bottlenecks?

AI inference involves significant coordination work beyond just GPU computation. Tasks like tokenization, batch scheduling, kernel launches, and inter-process communication all run on CPUs. As model sizes grow and inference becomes distributed across multiple GPUs, this coordination overhead increases, making CPU performance critical to overall system latency.

How much does CPU allocation affect AI inference performance?

Research shows dramatic effects. Moving from minimal to abundant CPU allocation reduced time-to-first-token by 1.36 to 5.40 times in 4-8 GPU LLM servers. In decode-heavy workloads, host overhead can dominate latency, with 10 decode tokens taking 188 ms versus 22 ms for prefill in one study.

What specific CPU features matter most for AI workloads?

Memory bandwidth (for moving model parameters and activations), I/O capacity (PCIe lanes for GPU connectivity), single-thread performance (for scheduling latency), and core count (for parallel coordination tasks) are all critical. Arm's new designs emphasize these areas with specifications like 12 DDR5 channels and 96 PCIe Gen6 lanes.

Will Arm-based servers really challenge x86 dominance in AI data centers?

The current x86 supply constraints create a practical opening for alternatives. Arm's architectural focus on memory bandwidth and I/O aligns well with AI coordination workloads. While ecosystem compatibility remains a hurdle, the performance requirements of AI inference may justify architectural transition where traditional enterprise workloads did not.