New research from NVIDIA suggests that artificial intelligence can be applied to optimize foundational Electronic Design Automation (EDA) tools, a domain historically reliant on expert human tuning. The work specifically targets tools like ABC, a widely-used system for logic synthesis and verification that has been manually optimized over decades by engineers.

Key Takeaways

- New NVIDIA research indicates AI can be used to optimize Electronic Design Automation (EDA) tools, such as the classic ABC system, which have been manually tuned by engineers for decades.

- This could automate a core, labor-intensive bottleneck in semiconductor design.

What Happened

A research paper from NVIDIA, highlighted by the dair_ai community, presents findings that AI techniques can be used to improve the performance of established EDA software. These tools, critical for designing and verifying integrated circuits, have traditionally been fine-tuned through a painstaking, iterative process by human experts. The research demonstrates a pathway to automating this optimization, potentially leading to more efficient tools and faster design cycles.

Context

Electronic Design Automation is the backbone of semiconductor engineering. Tools like ABC (developed at UC Berkeley) are used for tasks such as logic synthesis—converting high-level hardware descriptions into optimized gate-level netlists. Their performance directly impacts the power, performance, and area (PPA) of final chips. Optimizing these tools is a complex, multi-dimensional problem that has resisted full automation until now.

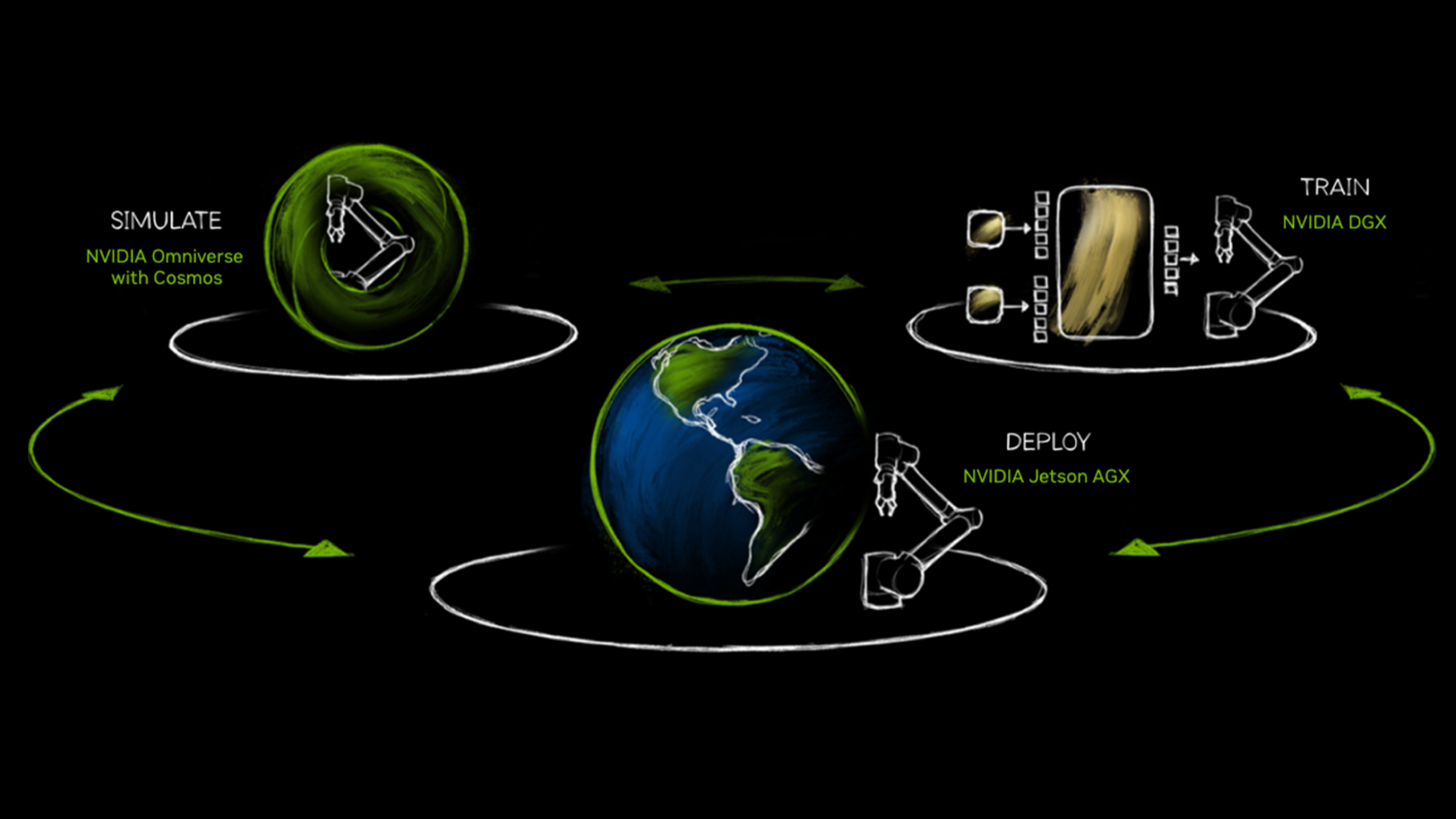

The application of AI/ML to chip design is not new; NVIDIA itself has pioneered its use with tools like NVIDIA cuLitho for computational lithography and has integrated AI into various stages of the design flow. However, targeting the optimization of the EDA tools themselves, rather than just using them as black boxes, represents a deeper layer of automation.

How It Might Work (Inference from the Field)

While the specific paper details are not provided in the source, typical approaches in this domain involve using reinforcement learning (RL) or Bayesian optimization to tune the myriad heuristics and parameters within an EDA tool. For a tool like ABC, an AI agent could be trained to select optimal sequences of logic optimization commands or tune internal algorithmic thresholds, with the goal of minimizing circuit delay or area across a benchmark suite of designs. The "reward" would be improved PPA metrics.

Potential Impact

If scalable, this approach could:

- Accelerate EDA Development: Reduce the time required to improve tool performance from human-led cycles to automated, continuous optimization.

- Democratize Expertise: Capture the tacit knowledge of expert tuners into AI models, making high-level optimization more accessible.

- Create Adaptive Tools: Generate tool configurations specialized for particular design styles (e.g., high-performance vs. ultra-low-power) without manual intervention.

The key challenge will be generalizability—ensuring optimizations learned from training benchmarks translate robustly to novel, real-world chip designs.

gentic.news Analysis

This research direction is a logical and significant next step in NVIDIA's long-term strategy to vertically integrate AI into every layer of the semiconductor ecosystem. NVIDIA isn't just building AI chips; it's using AI to build chips better and, as this paper suggests, to build better tools for building chips. This creates a compounding advantage.

It directly follows NVIDIA's established pattern of applying its core AI competency to adjacent hard problems in computing. We previously covered the launch of NVIDIA NeMo Curator, which uses AI to curate training data, and their work on EvoDiff, a generative AI for protein sequences. The through-line is the use of generative and optimization models to master complex, non-differentiable systems—whether they are biological sequences, datasets, or, as here, the heuristic-filled software of chip design.

This move also strategically reinforces NVIDIA's position against competitors in the EDA space, notably Cadence and Synopsys, who are also aggressively integrating AI into their platforms (e.g., Synopsys DSO.ai, Cadence Cerebrus). By researching how to optimize the tools themselves, NVIDIA is working at a meta-level that could eventually influence or disrupt the traditional EDA vendor landscape. It underscores that the future of chip design is not just AI-assisted, but AI-driven, from the ground up.

Frequently Asked Questions

What is ABC in chip design?

ABC is an open-source software system for sequential logic synthesis and formal verification of digital circuits. Developed at UC Berkeley, it's a foundational academic and industrial tool used to optimize and verify gate-level netlists, impacting the final chip's power, performance, and area.

How is AI currently used in EDA?

AI is currently used in several EDA stages: for predictive placement and routing (e.g., Synopsys DSO.ai), analog design migration, design space exploration, and verification test generation. It primarily helps navigate vast solution spaces faster than traditional algorithms or human designers alone.

What is the difference between using AI in EDA vs. using AI on EDA tools?

Using AI in EDA means employing AI models as a component within the design flow (e.g., an AI placer). Using AI on EDA tools, as suggested by this NVIDIA research, means applying AI to automatically configure, tune, and optimize the EDA software's own internal algorithms and parameters, which have traditionally been set by human experts.

Why is optimizing EDA tools like ABC so difficult?

Optimizing EDA tools is difficult because they rely on complex, interdependent heuristics to solve NP-hard problems. Changing one parameter can have unpredictable, non-linear effects on final circuit quality. This requires deep domain expertise and extensive manual benchmarking, making the process slow and expensive to automate with conventional programming.